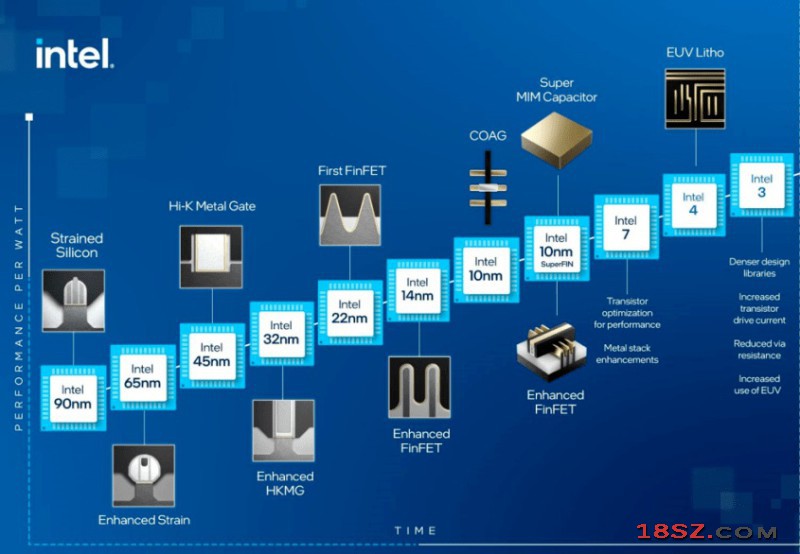

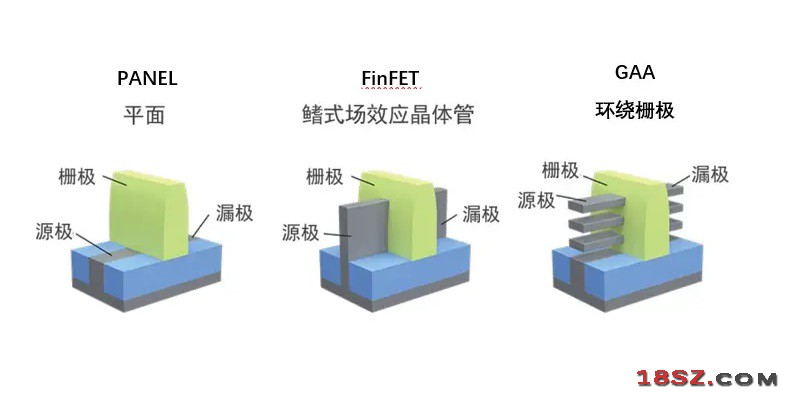

FinFET 于十多年前推出,并重新定义了芯片设计。非平面晶体管仍然被认为是非官方的行业标准,但向更新的技术——Gate-All-Around (GAA) 的过渡可能会加速。电子工程师需要为即将到来的变化做好准备。

第一批基于 FinFET 的芯片于 2011 年出现,使半导体进入 25 纳米以下工艺领域。这种架构在当时是对“摩尔定律”的一种救赎。这是因为平面晶体管的漏电流太大,无法在 100 纳米以下的几何结构中维持。

然而,FinFET 目前面临着与其平面前辈相同的问题。随着设备外形尺寸的不断缩小和性能要求的不断提高,泄漏功率和信号干扰问题正成为常见的障碍。因此,半导体行业的许多主要参与者开始考虑替代晶体管架构。

FinFET 比其前身更有用,但其较小的几何形状带来了严格的电源布线限制。工程师通常使用不同的通道宽度和间距来解决这一限制。尽管这种策略在许多应用中都能很好地发挥作用,但它也有局限性。

由于FinFET的结构,需要保证每个通道之间有足够的空间。因此,由于每个鳍片间距在 15 纳米到 20 纳米之间,工程师很快就会遇到可扩展性问题。添加更多通道意味着添加更多非活动区域,从而在当前路由和物理空间之间进行权衡。

GAA 晶体管作为一种解决方案应运而生。

什么是GAA FET(环绕栅极场效应晶体管)?

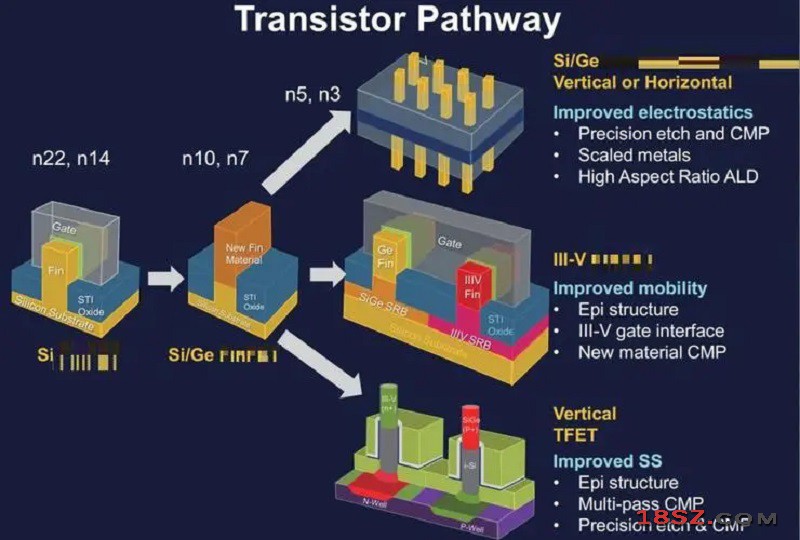

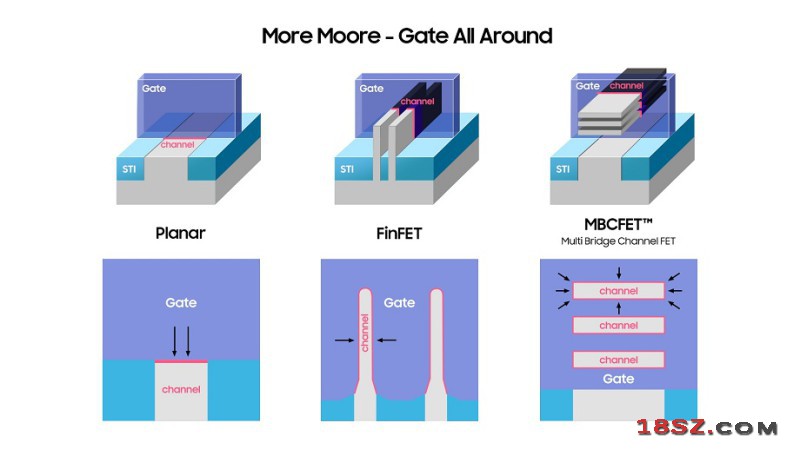

数字芯片最基本单元是MOSFET,其工艺发展到7nm、3nm、2nm,这个半导体工艺尺寸是MOSFET栅极(沟槽)宽度。早期MOSFET使用平面结构,沟槽宽度越小,漏极到源极距离越小,载流子流动跨越沟道导通时间减小,工作频率越高;同时,沟道完全开通所加栅极电压越低,开关损耗越低;而且,沟道导通电阻降低,导通损耗也降低。

但是,工艺尺寸越低,短沟道效应越明显。短沟道效应就是晶胞单元漏极到源极间距不断减小,栅极下部接触面积越来越小,栅极难以耗尽沟道载流子,其对沟道控制力不断减弱;因此,器件处于截止状态时漏电流会急剧增加,恶化其性能,静态功耗增加。

如果采用立体结构,增加栅极和沟道接触面积,如新的FinFET鳍型三维结构,就是将栅极包裹三个侧面沟道,就可以解决上述问题。为了进一步提高栅极对沟道控制能力,缩小单元尺寸,降低电压,GAA栅极环绕结构被开发出来。

GAA栅极环绕晶体管结构的栅极在垂直方向被分成几个条带RibbonFET,在其沟道区域,大幅增强对载流子控制,从而实现更好性能,同时也更容易优化工艺。

GAA纳米片FET的集成

GAA纳米片FET的集成涉及几个新步骤,需要一系列创新才能实现该技术。关键集成模块如下:

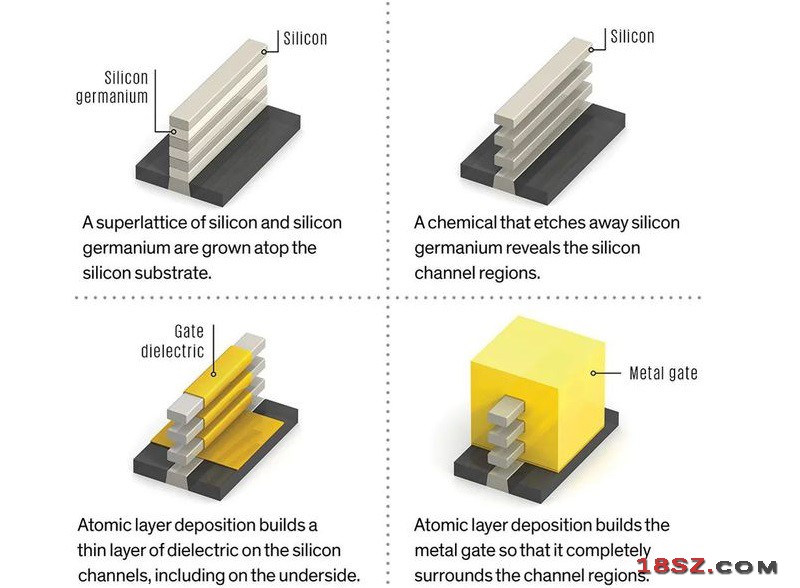

堆叠纳米片的形成:在Si衬底上外延生长SiGe和Si叠层;每层厚度均可高精度控制。

Fin reveal 和 STI:器件采用光刻方式定义,并执行浅沟槽隔离以隔离相邻器件。

伪栅极形成:形成多晶硅伪栅极以实现下游加工。

内间隔层和结形成:n 型或 p 型源/漏外延层选择性地形成在暴露的纳米片末端的任一侧。

替换金属栅极成型:

虚拟门拉:虚拟门被蚀刻出来,露出一个空腔,在空腔底部放置纳米片

牺牲SiGe通道释放:纳米片之间的SiGe通道被蚀刻掉,使高k金属栅极填充

形成高k金属栅极(HKMG):界面氧化物,高k介电层,n型或p型功函数被选择性沉积。

全底部介质隔离

为了介绍这个问题,我们首先介绍GAA纳米片特有的“肥鳍”效应,其中工艺不理想会导致结构,导致纳米片以下体区的电容增加。虽然这种结构是GAA纳米片所特有的,但这种效应也称为sub-fin泄漏,存在于FinFET中,并使用穿通阻挡器方案来处理。因此,基于断态泄漏电流、短沟道效应和有效电容(Ceff)对PTS方案与新型BDI方案进行了比较;结果表明,BDI有可能提供改进的Ceff和功率性能联合优化。

集成全底介电隔离需要在Si,、SiGe纳米片堆栈的底部添加高浓度的SiGe层。添加这一层,然后选择性地蚀刻它,需要降低用于纳米片堆叠的SiGe层中的Ge浓度。这引入了Si和SiGe之间较低的选择性,导致在SiGe通道移除过程中Si的损失,需要仔细考虑堆栈厚度,以确保TSi在整个工艺流程结束时不会太薄。我们可以在图3b中看到BDI位于S/D区域下方。

启用多个阈值电压

能够整合多个阈值电压(VT)是一项技术成为行业标准的关键要求。鉴于GAA FET的独特结构,沉积功函数金属的空间是有限的,替换金属栅极工艺仅使 Si 通道和内部间隔物之间的空间保持开放状态——根据技术要求填充功函数金属。这个空间,也称为Tsus(参见图2),可以通过控制在纳米片堆栈开发模块期间生长的SiGe层的厚度来控制,但仍然受到高度限制,必须仔细设计以满足器件产品的行业标准。

提出了两种不同的方法来适应GAAFET中的多VT产品——(1)WFM修改和(2)Tsus修改。图8给出了WFM修改的流程概述。VT调制的集成序列突出的挑战之一是,当WFM在Si通道之间被夹断时,大的Wsheet增加了WFM蚀刻的工艺挑战。为了克服这一点,参考文献提出用易于蚀刻的牺牲材料填充片与片之间的空间,选择性地打开其中一个FET,蚀刻掉已经沉积的工作功能金属。该方案不确定p型或n型WFM,并支持PG (p-FET优先)和MY (n-FET优先)方案。同样的过程可以重复来实现不同的功函数金属集,或者实现具有两个以上WFM的不同堆栈。

第二种方法需要在纳米片形成过程中通过改变沟道层外延厚度来改变Tsus。片间更大的空间允许在该空间中沉积更大体积的功功能金属,从而调节VT。与FinFET相比,这种设计按钮是GAA纳米片FET所特有的,因此,在这些纳米片FET中为多VT选项提供了更多的设计空间。

无体积多阈值电压

无体积多VT是一个术语,定义为表示基于偶极子的VT选项,其中形成了厚度小于5 Åis的偶极子,然后是基功函数金属。如引用的文献所示,这种创新方案提供了空间和栅极阻力方面的优势。然而,这种方法并不能直接从FinFET转化为GAA纳米片FET,因此参考文献中提出了专用的无体积VT集成。此外,无体积VT还有助于VT均匀性,这对晶体管的均匀开关很重要。

使用新颖的集成序列和GAA纳米片FET的独特设计按钮创建了几种不同口味的VT -(a) Tsus设计;和(b) WFM夹断。提出了一种基于偶极子的纳米FET VT结构。除了这些旋钮外,第4节中讨论的TSi设计还可以进行调制,以在移动性和短通道效应之间进行权衡。因此,总的来说,GAA纳米片FET为基于应用的优化提供了几个机会,因此它们适用于高功率和低功率应用。

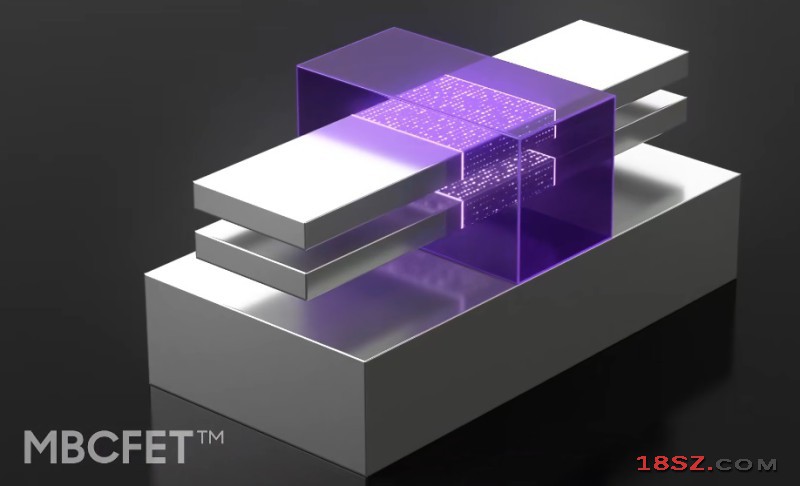

三星深度布局GAA 工艺

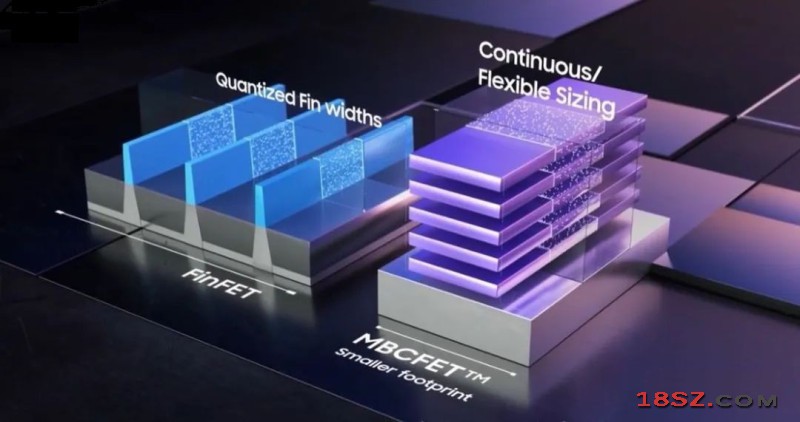

2022年六月,三星宣布已开始了采用环栅 (GAA) 晶体管架构的 3 纳米 (nm) 工艺节点的初始生产。其中用到的多桥通道 FET (MBCFET ) 是三星首次采用的 GAA 技术,该工艺突破了 FinFET 的性能限制,通过降低电源电压水平提高功率效率,同时还通过增加驱动电流能力提高性能。该公司也正在开始将纳米片晶体管与半导体芯片一起用于高性能、低功耗计算应用,并计划扩展到移动处理器。

三星表示,借助公司专有技术利用具有更宽通道的纳米片,与使用具有更窄通道的纳米线的 GAA 技术相比,可实现更高的性能和更高的能效。利用 3nm GAA 技术,三星将能够调整纳米片的通道宽度,以优化功耗和性能,以满足各种客户需求。

此外,GAA 的设计灵活性非常有利于设计技术协同优化 (DTCO),这有助于提高功率、性能、面积 (PPA) 优势。与5nm工艺相比,第一代3nm工艺相比5nm功耗最高可降低45%,性能提升23%,面积减少16%,而第二代3nm工艺则功耗最高可降低50%,性能提高 30%,面积减少 35%。

自 2019 年他们最初宣布该技术以来,三星一直致力于 3nm/GAAFET 技术的研发。三星特有的 GAA 晶体管技术是多桥通道 FET (MBCFET),这是一种基于纳米片的实现。基于纳米片的 FET 高度可定制,纳米片的宽度是定义功率和性能特征的关键指标:宽度越大,性能越好(在更高功率下)。因此,专注于低功耗的晶体管设计可以使用更小的纳米片,而需要更高性能的逻辑可以使用更宽的纳米片。

台湾媒体报道称,台积电的3纳米工艺生产良率高达85%,高于三星。但韩国业内消息人士淡化了这份报告,称这个数字似乎被夸大了。他们表示,考虑到台积电向苹果提供业界最小芯片的量产和交付时间表,其生产良率最多为50%。

按照媒体所说,因为在第一代3nm上折戟,三星正在大力投入到第二代工艺的研发中。

报告披露,三星第二代3nm GAA 工艺将会在2024年量产,工艺将加入MBCFET 架构,性能也将提升不少。虽然三星并没有分享4nm 节点的统计差异,但与该公司5nm 工艺相比,第二代3nm GAA 仍有望降低多达50% 的功耗、提升30% 性能、以及减少35% 的晶片面积占用。

美国据报拟进一步限制中国取得GAA技术

美中贸易战冲突未歇,传出美国将再次出手打击中国半导体产业,针对最新的环绕栅极晶体管(GAA)技术祭出限制措施,限制其获取人工智能(AI)芯片技术的能力,换言之,美国将防堵中国取得先进芯片,扩大受管制的范围。

美国财经媒体引述知情人士消息报导,拜登政府考虑新一波的半导体限制措施,以避免中国能够提升技术,进而增强军事能力,有可能限制中国取得GAA技术,但确切状况仍得等官方进一步说明,且不清楚官员何时会宣布新措施。

若此事成真,中国发展先进半导体将大受打击。目前三星从3奈米开始使用GAA技术,台积电则从2奈米制程才会转进GAA技术,预计2025年量产,现阶段3奈米仍采用鳍式场效晶体管(FinFET)制程技术。

三星3奈米制程已经于2022年6月量产,台积电3奈米虽晚了一些,但良率与性能评价比三星好上许多,包括大客户苹果包下首批产能,且高通、辉达与超威也都出手吃下后续产能。

EDN Taiwan电子技术设计杂志则介绍GAA技术,透过降低供电电压级以及增加驱动电流能力以提升性能,从而突破FinFET的性能限制。简言之,GAA技术让晶体管得以承载更多电流,同时保持相对较小。

Iteca Exhibitions

Iteca Exhibitions 长城润滑油

长城润滑油 German Machine Tool Builders Association

German Machine Tool Builders Association 延长石油

延长石油 3M制造业

3M制造业 陕煤化工集团

陕煤化工集团 HUAWEI

HUAWEI Dahua Technology

Dahua Technology 中国石油

中国石油 Gemtique

Gemtique KUNVII

KUNVII IAA Show

IAA Show PALEXPO

PALEXPO LASTON

LASTON 中杭贸易

中杭贸易 Etek Europe

Etek Europe PV EXPO

PV EXPO 陕西有色金属

陕西有色金属 QIIE青岛进博会

QIIE青岛进博会 维远光伏产业

维远光伏产业 Time Out Group

Time Out Group IFEMA

IFEMA 天元化工

天元化工 National Media

National Media 吉祥星科技

吉祥星科技 Dowpol Chemical

Dowpol Chemical 海康威视-HIK VISION

海康威视-HIK VISION Hannover Messe

Hannover Messe TOSHIBA

TOSHIBA Productronica

Productronica HealthCare

HealthCare 深圳会展中心

深圳会展中心 大唐旗舰店

大唐旗舰店 Soul Game

Soul Game 神木职教中心

神木职教中心 Sinopec

Sinopec 中国空间站首次出舱活动实况:航天员出舱视频

中国空间站首次出舱活动实况:航天员出舱视频 拉斯维加斯公务航空会议展

拉斯维加斯公务航空会议展 Optatec 2022

Optatec 2022 前海深港合作区成立10周年

前海深港合作区成立10周年 刘向明历史主题作品展南山文化馆开幕

刘向明历史主题作品展南山文化馆开幕 翰墨飘香歌盛世 丹青亮彩写岭南

翰墨飘香歌盛世 丹青亮彩写岭南 深圳最新国际形象片《深圳更深处》全球首发!

深圳最新国际形象片《深圳更深处》全球首发! 从设计到体验 全方位感受最真实的DS

从设计到体验 全方位感受最真实的DS 比利时布鲁塞尔巨幅海报为抗击疫情加油

比利时布鲁塞尔巨幅海报为抗击疫情加油 广东工业大学大学城校区图书馆五层书架

广东工业大学大学城校区图书馆五层书架 2020印度嵌入式展设计图

2020印度嵌入式展设计图 翰墨清逸 执着于心-著名画家崔培鲁作品赏析

翰墨清逸 执着于心-著名画家崔培鲁作品赏析 北京2022官方特许商品零售店玲珑塔店正式开业

北京2022官方特许商品零售店玲珑塔店正式开业 2019年曼谷国际光学眼镜展览会

2019年曼谷国际光学眼镜展览会 疫情下的美国首都华盛顿民众

疫情下的美国首都华盛顿民众 北宋剔刻的极致之美—登封白沙窑

北宋剔刻的极致之美—登封白沙窑 麂皮绒-星空

麂皮绒-星空 上海医疗用品展2023年医博会

上海医疗用品展2023年医博会 ART BASIN 8072

ART BASIN 8072 SQUATTING PAN ZT-409

SQUATTING PAN ZT-409 智慧医院物流传输解决方案

智慧医院物流传输解决方案 DROP EARRINGS

DROP EARRINGS 2025健康展-第34届北京国际大健康展|CIHIE·健博会

2025健康展-第34届北京国际大健康展|CIHIE·健博会 ONE-PIECE TOILET ZT-071

ONE-PIECE TOILET ZT-071 意大利里米尼城市介绍

意大利里米尼城市介绍 纽伦堡 - 玩具都城

纽伦堡 - 玩具都城 慕尼黑 - 伊萨尔河畔的酒都

慕尼黑 - 伊萨尔河畔的酒都 法兰克福 - 欧洲金融中心

法兰克福 - 欧洲金融中心 迪拜 - Dubal

迪拜 - Dubal 俄罗斯 - 战斗民族和套娃的国家

俄罗斯 - 战斗民族和套娃的国家 葡萄牙 - 软木塞之乡

葡萄牙 - 软木塞之乡 西班牙 - 斗牛士的故乡

西班牙 - 斗牛士的故乡