组合式的小芯片制造成本相对较低,良率更高,稳定性亦佳。(图/Shutterstock)

近两年半导体业界出现一种称为晶粒(chiplet)或小芯片的技术,使用先进的封装技术连接功能不同的数个芯片,让它可以赶上或超越最先进制程芯片的工作效率,并降低制造成本。这种半导体技术前景不仅被业界看好,更重要的是可以绕开芯片制程工艺的极限,对中国来说,更是突破美国芯片技术禁运一条极有希望的捷径。

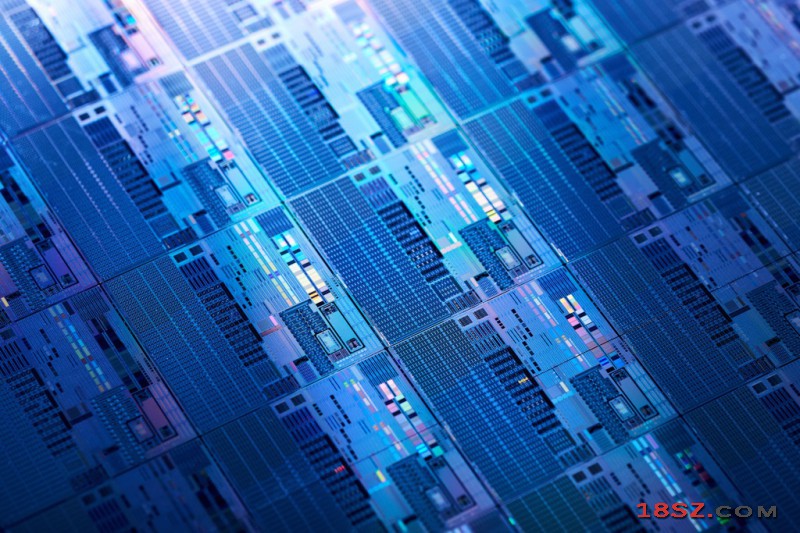

半导体制程多年来按着「摩尔定律」的法则逐渐进化,不断缩小晶体管尺寸,增加芯片内晶体管数目,但在芯片制程工艺不断发展下,晶体管微细化已逐渐接近物理极限,升级的技术愈加困难,制造成本亦快速飚升。科技界便尝试其他不同制造高性能芯片的途径,其中小芯片就是极被看好的新技术。

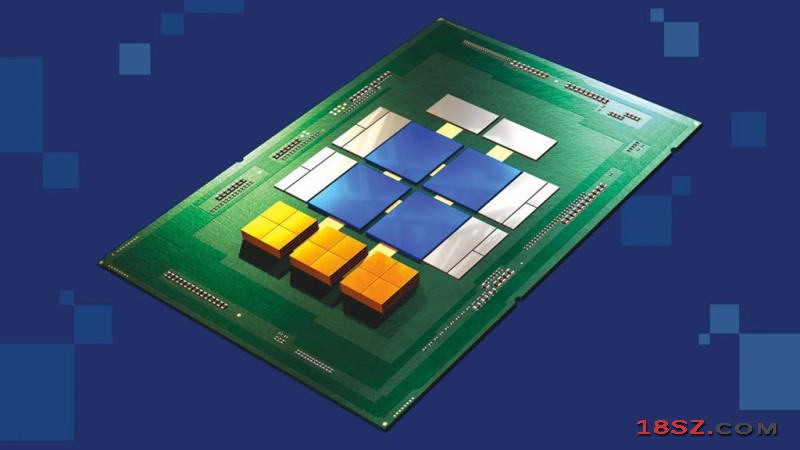

英特尔宣布联手台积电、三星、高通及日月光投控等半导体大厂,共组UCIe产业联盟。图为小芯片结构示意图。(图/英特尔)

小芯片的概念是不执着将所有的晶体管全部整合在一块芯片内,而是将多个功能相异的芯片透过先进封装技术整合在一起,形成一个系统芯片。如此可以不用太顶尖的芯片制程就能完成性能上的要求,能降低制造成本,还能提高芯片的良率。其中技术较困难的是芯片封装技术,不过相对于10nm以下的尖端芯片制程工艺来说,改进封装技术是容得得多,近年来这方面也有飞快进展。

吉尔辛格不久前宣布小芯片设计的最新构架和封装技术,扬言要引领芯片制造的新时代。(图/英特尔)

美国英特尔(Intel)执行长吉尔辛格(Pat Gelsinger)不久前宣布2.5D和3D芯片块(tile)设计的最新构架和封装技术创新,扬言要引领芯片制造的新时代。台积电、高通等半导体企业以及谷歌、微软等IT巨头在内的10家企业就小芯片技术展开合作,公开了通用小芯片互联标准「UCIe」,还成立了以实现标准化和构建生态系统为目标的产业联盟。

日本半导体界亦相当积极,东京工业大学开发模压树脂封装技术与硅基板中介层,而且还结合大阪大学、东北大学与30家企业组成「小芯片整合平台联盟」,以学术科研与企业界力量共同开发新一代的芯片整合技术。他们认为,日本的优势在于半导体材料和设备,这些都是发展小芯片技术的重要环节。

半导体业界一种称为晶粒或小芯片的技术,它使用先进的封装技术连接功能不同的数个芯片,让它可以赶上或超越最先进制程芯片的工作效率。(图/Shutterstock)

至于全球最大半导体市场的中国大陆则有另一套想法,目前美国芯片法案对中国实施14nm以下的半导体与其制造设备禁运,小芯片技术可以绕开制程工艺的限制,以14nm以上的半导体设备就能制造出所需要的最尖端、功能最强大的整合式小芯片。虽然目前先进的芯片封装技术仍落后于西方国家,但封装技术的差距比起芯片制程工艺差距要小得很多,较容易追赶得上,而且没有制造设备被「卡脖子」的问题。因此大陆业界认为,小芯片的技术路线不必再受限于14nm的制程限制,不只能够借此突破美方的芯片技术封锁,更有机会在半导体产业进行弯道超车。

据总部设于英国的产业咨询公司Omdia发表的报告,到2024年,小芯片的市场规模将达到58亿美元,2035年则超过570亿美元,亦即10年间可望成长近10倍。随着先进芯片制程工艺造成的技术障碍愈来困难,制造快速成本攀升,小芯片的技术路线不只能逐渐取代市场上采用先进制程的消费性半导体,长此以往,更能应对未来需要大量运算能力的人工智慧、超级电脑等产业的需求,市场前景无限广阔。

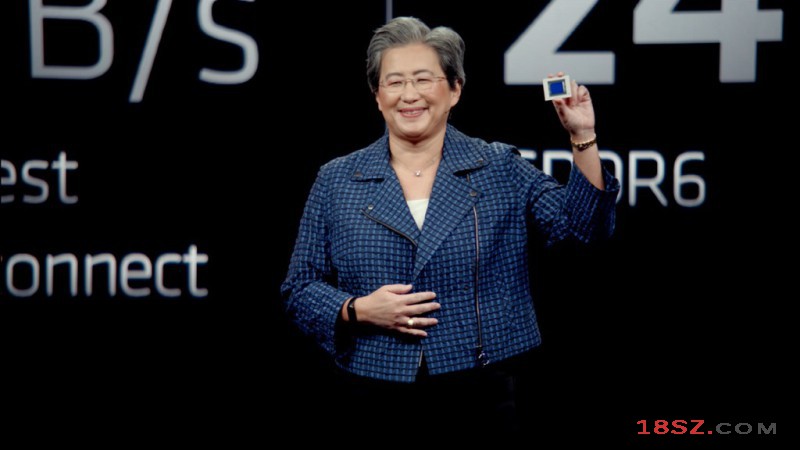

超威董事长暨执行长苏姿丰首度展示全球首款采用AMD小芯片设计的RDNA 3构架绘图处理器。(图/AMD)

有半导体产业分析认为,目前这个全球瞩目的产业正在进入一个新的黄金时代,这个时代的芯片制造将从传统晶圆代工模式转变成「系统晶圆代工」模式。届时半导体业的跨界整合将成为竞争的主战场,除了晶圆代工之外,封装技术与软件也会是市场竞争不可或缺的整合力量,大型企业的动向与政府政策介入将是左右未来半导体产业版图的主要力量,这种型态对中国政府与产业关系来说,也格外地有利。

Iteca Exhibitions

Iteca Exhibitions 长城润滑油

长城润滑油 German Machine Tool Builders Association

German Machine Tool Builders Association KUNVII

KUNVII 3M制造业

3M制造业 延长石油

延长石油 Time Out Group

Time Out Group HUAWEI

HUAWEI 陕煤化工集团

陕煤化工集团 Dahua Technology

Dahua Technology Dowpol Chemical

Dowpol Chemical Gemtique

Gemtique National Media

National Media 中国石油

中国石油 PV EXPO

PV EXPO 中杭贸易

中杭贸易 Etek Europe

Etek Europe IAA Show

IAA Show LASTON

LASTON PALEXPO

PALEXPO QIIE青岛进博会

QIIE青岛进博会 陕西有色金属

陕西有色金属 天元化工

天元化工 维远光伏产业

维远光伏产业 海康威视-HIK VISION

海康威视-HIK VISION 健麾信息

健麾信息 吉祥星科技

吉祥星科技 IFEMA

IFEMA 深圳会展中心

深圳会展中心 TOSHIBA

TOSHIBA Hannover Messe

Hannover Messe Sinopec

Sinopec Productronica

Productronica HealthCare

HealthCare Soul Game

Soul Game 大唐旗舰店

大唐旗舰店 世贸组织上诉机构停摆 美阻挠引不满

世贸组织上诉机构停摆 美阻挠引不满 记者带你去看澳门光影节 五彩斑斓

记者带你去看澳门光影节 五彩斑斓 项圈变胸针拆装视频

项圈变胸针拆装视频 25吨深圳口罩登上飞机客舱 探秘波音787如何快速变身

25吨深圳口罩登上飞机客舱 探秘波音787如何快速变身 车载V型花水晶旗摆件

车载V型花水晶旗摆件 2021中国国际智能产业博览会开幕

2021中国国际智能产业博览会开幕 中国空间站首次出舱活动实况:航天员出舱视频

中国空间站首次出舱活动实况:航天员出舱视频 时尚与艺术的完美演绎,这么别具一格的时装秀你一定没看过!

时尚与艺术的完美演绎,这么别具一格的时装秀你一定没看过! 2021年莫斯科国际化工展览会

2021年莫斯科国际化工展览会 Exhibit at Achem Asia

Exhibit at Achem Asia 2020年欧洲集成系统及技术展览会参展现场

2020年欧洲集成系统及技术展览会参展现场 匠心漆韵——金漆镶嵌技艺精品展在京开幕

匠心漆韵——金漆镶嵌技艺精品展在京开幕 中印边境撤军后班公湖最新卫星照曝光

中印边境撤军后班公湖最新卫星照曝光 德国科隆狂欢节举办“玫瑰星期一”大游行

德国科隆狂欢节举办“玫瑰星期一”大游行 泉城济南:济西湿地春色美

泉城济南:济西湿地春色美 深美闳约:宝能第一空间联展_西乐群山水作品

深美闳约:宝能第一空间联展_西乐群山水作品 2025年美国拉斯维加斯国际家具配件及木工机械展AWFS

2025年美国拉斯维加斯国际家具配件及木工机械展AWFS 长征者-老红军钟清才油画

长征者-老红军钟清才油画 2022空气净化展-2022中国国际环保技术设备展会

2022空气净化展-2022中国国际环保技术设备展会 国画微湖鸟石图

国画微湖鸟石图 2024 广州国际汽车电子技术展览会

2024 广州国际汽车电子技术展览会 2025年迪拜国际木工及木工机械展览会WOODSHOW

2025年迪拜国际木工及木工机械展览会WOODSHOW FFF2024第15届捷克(布拉格)国际防务与军警展

FFF2024第15届捷克(布拉格)国际防务与军警展 2024第四十四届深圳国际医疗器械展览会

2024第四十四届深圳国际医疗器械展览会 意大利里米尼城市介绍

意大利里米尼城市介绍 纽伦堡 - 玩具都城

纽伦堡 - 玩具都城 慕尼黑 - 伊萨尔河畔的酒都

慕尼黑 - 伊萨尔河畔的酒都 法兰克福 - 欧洲金融中心

法兰克福 - 欧洲金融中心 迪拜 - Dubal

迪拜 - Dubal 俄罗斯 - 战斗民族和套娃的国家

俄罗斯 - 战斗民族和套娃的国家 葡萄牙 - 软木塞之乡

葡萄牙 - 软木塞之乡 西班牙 - 斗牛士的故乡

西班牙 - 斗牛士的故乡