台积电先进封装技术暨服务副总经理廖德堆9月23日,在国际半导体产业协会(SEMI)举办的线上高科技智慧制造论坛上透露,台积电2020年制程技术已发展至五纳米,预计在2022年完成五纳米的SoIC开发。

据澎湃新闻报道,台积电先进封装采用系统整合单芯片(System-on-Integrated-Chips,SoIC),提供以五纳米以下为核心的小芯片(Chiplet)的整合解决方案。据介绍,台积电正在打造创新的3D Fabric先进封测制造基地,将三座厂房所组成。

随着芯片先进制程技术朝三纳米或以下推进时,具有先进封装的小芯片概念,已成为必要的解决方案。

廖德堆介绍,台积电的3D Fabric先进封测制造基地包括先进测试、SoIC和2.5D先进封装(InFO、CoWoS)厂房;其中的SoIC厂房将于今年导入机台,2.5D先进封装厂房预计明年完成。

据介绍,台积电已建构完整的3D Fabric生态系,包含基板、记忆体、封装设备、材料等。

目前台积电为苹果代工用于iPhone 13 A15处理器,正是采用台积电为苹果打造的五纳米强化版(N5P)制程,台积电即靠领先全球的3D Fabric平台,提供苹果从芯片制程到测试再到后段封装的整合解决方案。

Iteca Exhibitions

Iteca Exhibitions 长城润滑油

长城润滑油 German Machine Tool Builders Association

German Machine Tool Builders Association 延长石油

延长石油 3M制造业

3M制造业 陕煤化工集团

陕煤化工集团 HUAWEI

HUAWEI Dahua Technology

Dahua Technology 中国石油

中国石油 Gemtique

Gemtique KUNVII

KUNVII PALEXPO

PALEXPO IAA Show

IAA Show LASTON

LASTON 中杭贸易

中杭贸易 Etek Europe

Etek Europe PV EXPO

PV EXPO QIIE青岛进博会

QIIE青岛进博会 陕西有色金属

陕西有色金属 维远光伏产业

维远光伏产业 Time Out Group

Time Out Group IFEMA

IFEMA 天元化工

天元化工 National Media

National Media 吉祥星科技

吉祥星科技 Dowpol Chemical

Dowpol Chemical 海康威视-HIK VISION

海康威视-HIK VISION Hannover Messe

Hannover Messe TOSHIBA

TOSHIBA Productronica

Productronica HealthCare

HealthCare 深圳会展中心

深圳会展中心 大唐旗舰店

大唐旗舰店 Soul Game

Soul Game 神木职教中心

神木职教中心 Sinopec

Sinopec 深美闳约_宝能第一空间名家书画联展开幕现场

深美闳约_宝能第一空间名家书画联展开幕现场 伦敦国际军工及技术展览会( ITEC)

伦敦国际军工及技术展览会( ITEC) Guinness World Record Mudan

Guinness World Record Mudan 崔文僮讲解展厅精品国画

崔文僮讲解展厅精品国画 冬季入浴前需提前预热浴室

冬季入浴前需提前预热浴室 崔培鲁《艺术传承书画同源》画展采访

崔培鲁《艺术传承书画同源》画展采访 1980年中国创立了深圳、珠海、汕头、厦门经济特区

1980年中国创立了深圳、珠海、汕头、厦门经济特区 五月苏绣艺术品在线展示

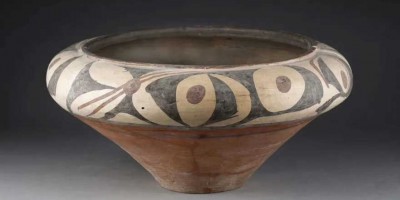

五月苏绣艺术品在线展示 花卉纹彩陶瓮

花卉纹彩陶瓮 国画牡丹图

国画牡丹图 景德镇薄胎瓷:0.15毫米的极致匠心

景德镇薄胎瓷:0.15毫米的极致匠心 中国共产党举行百年党庆大会

中国共产党举行百年党庆大会 割胶“黑科技”助力天然橡胶生产自动化

割胶“黑科技”助力天然橡胶生产自动化 陕西安塞改善设施农业促增收

陕西安塞改善设施农业促增收 DowSyn 改进剂

DowSyn 改进剂 Heyuan Textile Products

Heyuan Textile Products 2024年秋季广州美博会-2024年9月份广州美博会

2024年秋季广州美博会-2024年9月份广州美博会 2024 广州国际汽车电子技术展览会

2024 广州国际汽车电子技术展览会 2024上海国际智慧物业展览会

2024上海国际智慧物业展览会 船型翘板开关R-210-DR0L-BBR

船型翘板开关R-210-DR0L-BBR 2021第100届中国劳动保护用品交易会

2021第100届中国劳动保护用品交易会 智能换相器

智能换相器 2025北京国际信息通信展览会

2025北京国际信息通信展览会 IHE 2024第32届广州(国际)大健康产业博览会

IHE 2024第32届广州(国际)大健康产业博览会 意大利里米尼城市介绍

意大利里米尼城市介绍 纽伦堡 - 玩具都城

纽伦堡 - 玩具都城 慕尼黑 - 伊萨尔河畔的酒都

慕尼黑 - 伊萨尔河畔的酒都 法兰克福 - 欧洲金融中心

法兰克福 - 欧洲金融中心 迪拜 - Dubal

迪拜 - Dubal 俄罗斯 - 战斗民族和套娃的国家

俄罗斯 - 战斗民族和套娃的国家 葡萄牙 - 软木塞之乡

葡萄牙 - 软木塞之乡 西班牙 - 斗牛士的故乡

西班牙 - 斗牛士的故乡